[OS]Three Easy Pieces Chapter 19

Paging: Faster Translations (TLBs)

为了加速内存访问,OS需要硬件的帮助:translation-lookaside buffer(TLB)。TLB其实就是经常访问的PTE的硬件缓存。在每次访存之前,硬件首先去TLB中查看指定的PTE是否存在,如果存在,就不需要去内存中查找对应的PTE了。

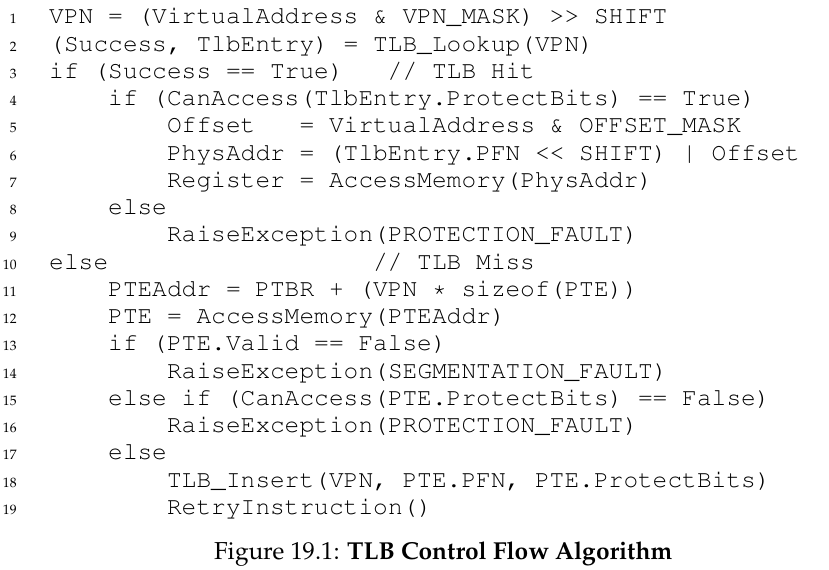

1 TLB Basic Algorithm

2 Who Handles The TLB Miss

硬件处理

由硬件负责更新TLB。

软件处理(OS)

由OS负责更新TLB。当遇到TLB miss的时候,硬件只需要发出一个异常,然后跳转到对应的异常处理程序进行处理即可。

注意事项:

- 这种异常和系统调用不一样,系统调用返回下一条指令的地址继续执行;而这种异常需要返回当前指令的地址重新执行当前指令。

- OS需要确保TLB miss处理代码不会触发TLB miss。可以直接将处理代码放在物理地址中(未映射,无需地址翻译)或者在TLB中预留一些entries用来存放处理代码的PTE。

3 TLB Contents: What’s In There

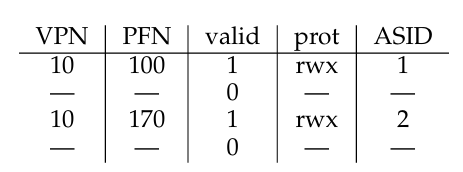

TLB通常有32,64,128个entries,并且是全相连的(意味着任何一个entry都可能防止在任何位置,由硬件负责并行的查找对应的entry)。

需要注意,TLB entry需要包含VPN,因为TLB是全相连的。

other bits通常包含valid bit,protection bits,address-space identifier,dirty bit等。

4 TLB Issue: Context Switches

需要注意的是,TLB中的内容都是针对某个进程而言的。当发生上下文切换的时候,TLB中的内容就不在有效了。

TLB flush

简单的做法是每次上下文切换的时候,都将TLB中的内容flush掉(将valid bit置0)。但是对于频繁切换的系统,可能会带来较大的开销。

ASID

另一种做法是在TLB entry中增加一个address space identifier(ASID)来指示该entry对应的进程。ASID相当于是PID,但是通常只有较少的位数(PID32位,ASID8位)

5 Issue: Replacement Policy

类似于页置换算法。

典型的有LRU,随机替换算法等。随机替换算法比较简单,并且可以避免一些边界情况。

[OS]Three Easy Pieces Chapter 19

https://erlsrnby04.github.io/2024/11/15/OS-Three-Easy-Pieces-Chapter-19/